AMD新处理器:跨CCD延迟大降,造价飙升?

时间:2025-01-15 15:03:00

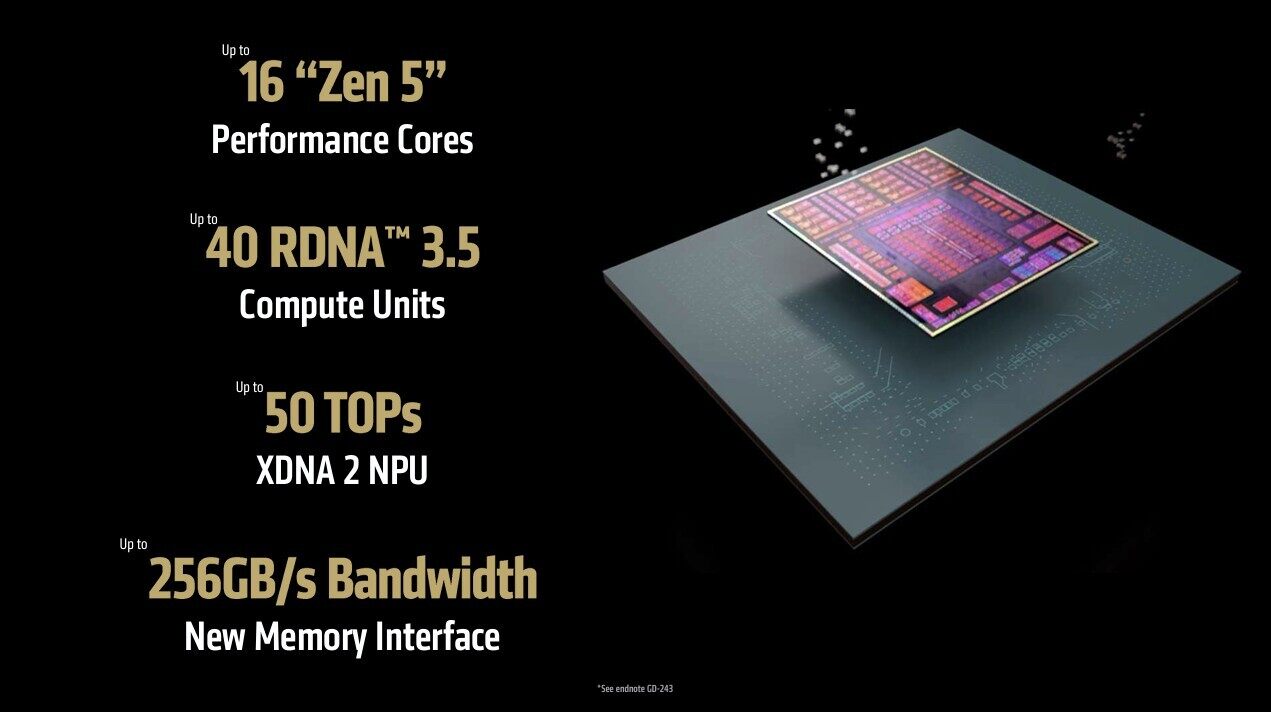

在 CES 2025 上,AMD 推出了代号为 Strix Halo 的 Ryzen AI MAX 300 系列高性能移动处理器,其拥有最高 16 核、32 线程的 CPU,以及 40 组 CU 的庞大 GPU。

外媒 Chips and Cheese 对 AMD 高级晶片研究工程师 Mahesh Subramony 进行了访问,为大家揭示 Ryzen AI MAX 300 处理器系列在开发与设计方面的幕后情况。

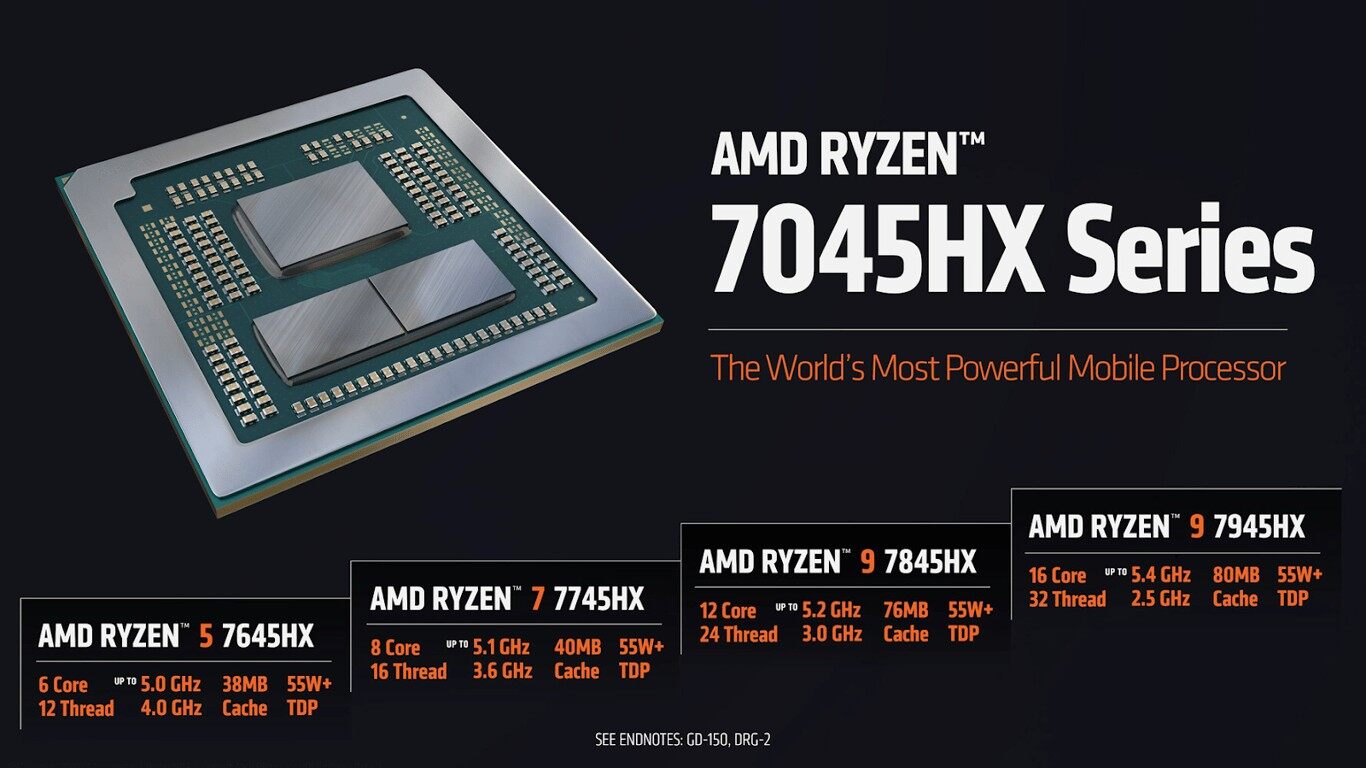

该系列处理器采用 Zen 5 架构及 Chiplet 小晶片设计,其中装载 CPU 核心的晶片被称作 CCD,每颗 CCD 可容纳 8 颗核心。因此,在像 Ryzen AI MAX + 395、AI MAX 390 这类核心数量超过 8 组的产品中,数据运算有时会出现跨 CCD 传输的现象。

长期以来,AMD 在跨 CCD 运算方面一直被指责延迟过高,原因在于 CCD 的连接方案,包括当下最新的 Ryzen 9000 桌上型系列,均采用 SERDES(Serializer / Deserializer,串行器/解码器)方案。

此方案的优点是能够允许更长的传输路径,但缺点是会增加延迟。然而,在 Ryzen AI 300 上,AMD 将连接方式改为“线路海”(Sea of wire)策略,通过大量电路直接连接每颗小晶片,取代原有的 SERDES 设计。

这种线路支持每个时钟周期 32 bytes 的资料吞吐量,并且由于减少了额外转换的步骤,使得 CCD 之间的传输更加高效,从而降低了延迟。当然,新的连接设计并非完美无缺。